# **PyRTL**

**Timothy Sherwood**

# **CONTENTS**

| 1  | Quick links                               | 3              |  |  |  |  |

|----|-------------------------------------------|----------------|--|--|--|--|

| 2  | Installation                              |                |  |  |  |  |

| 3  | Design, Simulate, and Inspect in 15 lines | 7              |  |  |  |  |

| 4  | Overview of PyRTL 4.1 PyRTL Classes:      | <b>9</b><br>9  |  |  |  |  |

| 5  | Reference Guide 5.1 Wires and Logic       | 11<br>11<br>18 |  |  |  |  |

|    | 5.3 Simulation and Testing                | 20<br>33<br>39 |  |  |  |  |

|    | 5.6 Analysis and Optimization             | 58<br>64<br>69 |  |  |  |  |

| 6  | Index                                     | 85             |  |  |  |  |

| Ру | ython Module Index                        | 87             |  |  |  |  |

| In | ndex                                      | 89             |  |  |  |  |

A collection of classes providing simple RTL specification, simulation, tracing, and testing suitable for teaching and research. Simplicity, usability, clarity, and extensibility rather than performance or optimization is the overarching goal. With PyRTL you can use the full power of Python to describe complex synthesizable digital designs, simulate and test them, and export them to Verilog.

CONTENTS 1

2 CONTENTS

# CHAPTER

# **ONE**

# **QUICK LINKS**

- Get an overview from the PyRTL Project Webpage

- Read through Example PyRTL Code

- File a Bug or Issue Report

- Contribute to project on GitHub

**CHAPTER**

**TWO**

# **INSTALLATION**

#### **Automatic installation:**

pip install pyrtl

PyRTL is listed in PyPI and can be installed with **pip** or **pip3**. If the above command fails due to insufficient permissions, you may need to do sudo pip install pyrtl (to install as superuser) or pip install --user pyrtl (to install as a normal user).

PyRTL is tested to work with Python 3.8+.

# **DESIGN, SIMULATE, AND INSPECT IN 15 LINES**

```

import pyrtl

2

a = pyrtl.Input(8, 'a') # input "pins"

b = pyrtl.Input(8, 'b')

q = pyrtl.Output(8,'q') # output "pins"

gt5 = pyrtl.Output(1,'gt5')

result = a + b # makes an 8-bit adder

q <<= result # assigns output of adder to out pin

gt5 <<= result > 5  # does a comparison, assigns that to different pin

10

11

# simulate and output the resulting waveform to the terminal

12

sim = pyrtl.Simulation()

13

sim.step_multiple({'a':[0,1,2,3,4], 'b':[2,2,3,3,4]})

sim.tracer.render_trace()

```

After you have PyRTL installed, you should be able to cut and paste the above into a file and run it with Python. The result you should see, drawn right into the terminal, is the output of the simulation. While a great deal of work has gone into making hardware design in PyRTL as friendly as possible, please don't mistake that for a lack of depth. You can just as easily export to Verilog or other hardware formats, view results with your favorite waveform viewer, build hardware transformation passes, run JIT-accelerated simulations, design, test, and even verify hugely complex digital systems, and much more. Most critically of all it is easy to extend with your own approaches to digital hardware development as you find necessary.

# **OVERVIEW OF PYRTL**

If you are brand new to PyRTL we recommend that you start with the PyRTL Code Examples which will show you most of the core functionality in the context of a complete design.

# 4.1 PyRTL Classes:

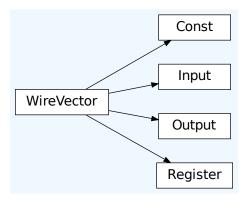

Perhaps the most important class to understand is <code>WireVector</code>, which is the basic type from which you build all hardware. If you are coming to PyRTL from Verilog, a <code>WireVector</code> is closest to a multi-bit <code>wire</code>. Every new <code>WireVector</code> builds a set of wires which you can then connect with other <code>WireVector</code> through overloaded operations such as <code>addition</code> or <code>bitwise or</code>. A bunch of other related classes, including <code>Input</code>, <code>Output</code>, <code>Const</code>, and <code>Register</code> are all derived from <code>WireVector</code>. Coupled with <code>MemBlock</code> (and <code>RomBlock</code>), this is all a user needs to create a functional hardware design.

After specifying a hardware design, there are then options to simulate your design right in PyRTL, synthesize it down to primitive 1-bit operations, optimize it, and export it to Verilog (along with a testbench).

# 4.1.1 Simulation

PyRTL provides tools for simulation and viewing simulation traces. Simulation is how your hardware is "executed" for the purposes of testing, and three different classes help you do that: Simulation, FastSimulation and CompiledSimulation. All three have almost the same interface and, except for a few debugging cases, can be used interchangeably. Typically one starts with Simulation and then moves up to FastSimulation when performance begins to matter.

Both Simulation and FastSimulation take an instance of SimulationTrace as an argument (or makes an empty SimulationTrace by default), which stores a list of the signals as they are simulated. This trace can then be rendered to the terminal with WaveRenderer, although unless there are some problems with the default configurations, most end users should not need to even be aware of WaveRenderer. The examples describe other ways that the trace may be handled, including extraction as a test bench and export to a VCD file.

# 4.1.2 Optimization

WireVector and MemBlock are just "sugar" over a core set of primitives, and the final design is built up incrementally as a graph of these primitives. WireVectors connects these "primitives", which connect to other WireVectors. Each primitive is a LogicNet, and a Block is a graph of LogicNets. Typically a full design is stored in a single Block. The function working\_block() returns the block on which we are implicitly working. Hardware transforms may make a new Block from an old one. For example, see PostSynthBlock.

# **4.1.3 Errors**

Finally, when things go wrong you may hit on one of two Exceptions, neither of which is likely recoverable automatically (which is why we limited them to only two). The intention is that PyrtlError is intended to capture end user errors such as invalid constant strings and mis-matched bitwidths. In contrast, PyrtlInternalError captures internal invariants and assertions over the core logic graph which should never be hit when constructing designs in the normal ways. If you hit a confusing PyrtlError or any PyrtlInternalError feel free to file an issue.

**CHAPTER**

**FIVE**

# **REFERENCE GUIDE**

# 5.1 Wires and Logic

Wires define the relationship between logic blocks in PyRTL. They are treated like normal wires in traditional RTL systems except the *Register* wire. Logic is then created when wires are combined with one another using the provided operators. For example, if a and b are both of type *WireVector*, then a + b will make an adder, plug a and b into the inputs of that adder, and return a new *WireVector* which is the output of that adder. *Block* stores the description of the hardware as you build it.

Input, Output, Const, and Register all derive from WireVector. Input represents an input pin, serving as a placeholder for an external value provided during simulation. Output represents an output pin, which does not drive any wires in the design. Const is useful for specifying hard-wired values and Register is how sequential elements are created (they all have an implicit clock).

# 5.1.1 WireVector

class pyrtl.wire.WireVector(bitwidth=None, name=", block=None)

The main class for describing the connections between operators.

WireVectors act much like a list of wires, except that there is no "contained" type, each slice of a WireVector is itself a WireVector (even if it just contains a single "bit" of information). The least significant bit of the wire is at index 0 and normal list slicing syntax applies (i.e. myvector[0:5] makes a new vector from the bottom 5 bits of myvector, myvector[-1] takes the most significant bit, and myvector[-4:] takes the 4 most significant bits).

| Operation       | Syntax  | Function                                              |

|-----------------|---------|-------------------------------------------------------|

| Addition        | a + b   | Creates an adder, returns WireVector                  |

| Subtraction     | a - b   | Subtraction (two's complement)                        |

| Multiplication  | a * b   | Creates an multiplier, returns WireVector             |

| Xor             | a ^ b   | Bitwise XOR, returns WireVector                       |

| Or              | a   b   | Bitwise OR, returns WireVector                        |

| And             | a & b   | Bitwise AND, returns WireVector                       |

| Invert          | ~a      | Bitwise invert, returns WireVector                    |

| Less Than       | a < b   | Less than, return 1-bit WireVector                    |

| Less or Eq.     | a <= b  | Less than or Equal to, return 1-bit WireVector        |

| Greater Than    | a > b   | Greater than, return 1-bit WireVector                 |

| Greater or Eq.  | a >= b  | Greater or Equal to, return 1-bit WireVector          |

| Equality        | a == b  | Hardware to check equality, return 1-bit WireVector   |

| Not Equal       | a != b  | Inverted equality check, return 1-bit WireVector      |

| Bitwidth len(a) |         | Return bitwidth of the WireVector                     |

| Assignment      | a <<= b | Connect from b to a (see note below)                  |

| Bit Slice       | a[3:6]  | Selects bits from WireVector, in this case bits 3,4,5 |

A note on << asssignment: This operator is how you "drive" an already created wire with an existing wire. If you were to do a = b it would lose the old value of a and simply overwrite it with a new value, in this case with a reference to WireVector b. In contrast a <<= b does not overwrite a, but simply wires the two together.

#### **\_\_add\_\_**(*other*)

Creates a LogicNet that adds two wires together into a single WireVector.

# **Return WireVector**

Returns the result wire of the operation. The resulting wire has one more bit than the longer of the two input wires.

Addition is compatible with two's complement signed numbers.

#### Examples:

```

temp = a + b # simple addition of two WireVectors

temp = a + 5 # you can use integers

temp = a + 0b110 # you can use other integers

temp = a + "3'h7" # compatable verilog constants work too

```

# \_\_ilshift\_\_(other)

Wire assignment operator (assign other to self).

Example:

```

i = pyrtl.Input(8, 'i')

t = pyrtl.WireVector(8, 't')

t <<= i</pre>

```

```

__init__(bitwidth=None, name=", block=None)

```

Construct a generic WireVector.

#### **Parameters**

- **bitwidth** (*int*) If no bitwidth is provided, it will be set to the minimum number of bits to represent this wire

- block (Block) The block under which the wire should be placed. Defaults to the working block

- **name** (*str*) The name of the wire referred to in some places. Must be unique. If none is provided, one will be autogenerated

#### Returns

a WireVector object

#### Examples:

```

data = pyrtl.WireVector(8, 'data') # visible in trace as "data"

ctrl = pyrtl.WireVector(1) # assigned tmp name, not visible in traces by______

default

temp = pyrtl.WireVector() # temporary with width to be defined later

temp <<= data # this this case temp will get the bitwdith of 8 from data

```

#### \_\_len\_\_()

Get the bitwidth of a WireVector.

#### **Return integer**

Returns the length (i.e. bitwidth) of the WireVector in bits.

Note that WireVectors do not need to have a bitwidth defined when they are first allocated. They can get it from a <<= assignment later. However, if you check the len of WireVector with undefined bitwidth it will throw PyrtlError.

```

__mul__(other)

```

Creates a LogicNet that multiplies two different WireVectors.

# **Return WireVector**

Returns the result wire of the operation. The resulting wire's bitwidth is the sum of the two input wires' bitwidths.

Multiplication is *not* compatible with two's complement signed numbers.

```

__sub__(other)

```

Creates a LogicNet that subtracts the right wire from the left one.

# **Return WireVector**

Returns the result wire of the operation. The resulting wire has one more bit than the longer of the two input wires.

Subtraction is compatible with two's complement signed numbers.

#### property bitmask

A property holding a bitmask of the same length as this WireVector. Specifically it is an integer with a number of bits set to 1 equal to the bitwidth of the WireVector.

It is often times useful to "mask" an integer such that it fits in the the number of bits of a WireVector. As a convenience for this, the bitmask property is provided. As an example, if there was a 3-bit WireVector a, a call to a.bitmask() should return 0b111 or 0x7.

# property name

A property holding the name (a string) of the WireVector, can be read or written. For example: print(a. name) or a.name = 'mywire'.

#### nand(other)

Creates a LogicNet that bitwise nands two WireVectors together to a single WireVector.

#### **Return WireVector**

Returns WireVector of the nand operation.

# sign\_extended(bitwidth)

Generate a new sign extended WireVector derived from self.

#### **Return WireVector**

Returns a new WireVector equal to the original WireVector sign extended to the specified bitwidth.

If the bitwidth specified is smaller than the bitwidth of self, then PyrtlError is thrown.

#### truncate(bitwidth)

Generate a new truncated WireVector derived from self.

#### **Return WireVector**

Returns a new WireVector equal to the original WireVector but truncated to the specified bitwidth.

If the bitwidth specified is larger than the bitwidth of self, then PyrtlError is thrown.

# zero\_extended(bitwidth)

Generate a new zero extended WireVector derived from self.

#### **Return WireVector**

Returns a new WireVector equal to the original WireVector zero extended to the specified bitwidth.

If the bitwidth specified is smaller than the bitwidth of self, then PyrtlError is thrown.

# 5.1.2 Input Pins

class pyrtl.wire.Input(bitwidth=None, name=", block=None)

Bases: WireVector

A WireVector type denoting inputs to a block (no writers).

\_\_init\_\_(bitwidth=None, name=", block=None)

Construct a generic WireVector.

#### **Parameters**

- **bitwidth** (*int*) If no bitwidth is provided, it will be set to the minimum number of bits to represent this wire

- **block** (Block) The block under which the wire should be placed. Defaults to the working block

• **name** (*str*) – The name of the wire referred to in some places. Must be unique. If none is provided, one will be autogenerated

#### Returns

a WireVector object

### Examples:

```

data = pyrtl.WireVector(8, 'data') # visible in trace as "data"

ctrl = pyrtl.WireVector(1) # assigned tmp name, not visible in traces by_

default

temp = pyrtl.WireVector() # temporary with width to be defined later

temp <<= data # this this case temp will get the bitwdith of 8 from data

```

# 5.1.3 Output Pins

```

class pyrtl.wire.Output(bitwidth=None, name=", block=None)

Bases: WireVector

A WireVector type denoting outputs of a block (no readers).

Even though Output seems to have valid ops such as __or__ , using them will throw an error.

__init__(bitwidth=None, name=", block=None)

```

#### **Parameters**

Construct a generic WireVector.

- **bitwidth** (*int*) If no bitwidth is provided, it will be set to the minimum number of bits to represent this wire

- **block** (Block) The block under which the wire should be placed. Defaults to the working block

- **name** (*str*) The name of the wire referred to in some places. Must be unique. If none is provided, one will be autogenerated

#### Returns

a WireVector object

## Examples:

```

data = pyrtl.WireVector(8, 'data') # visible in trace as "data"

ctrl = pyrtl.WireVector(1) # assigned tmp name, not visible in traces by

default

temp = pyrtl.WireVector() # temporary with width to be defined later

temp <<= data # this this case temp will get the bitwdith of 8 from data

```

#### 5.1.4 Constants

class pyrtl.wire.Const(val, bitwidth=None, name=", signed=False, block=None)

Bases: WireVector

A WireVector representation of a constant value.

Converts from bool, integer, or Verilog-style strings to a constant of the specified bitwidth. If the bitwidth is too short to represent the specified constant, then an error is raised. If a positive integer is specified, the bitwidth can be inferred from the constant. If a negative integer is provided in the simulation, it is converted to a two's complement representation of the specified bitwidth.

```

__init__(val, bitwidth=None, name=", signed=False, block=None)

```

Construct a constant implementation at initialization.

#### **Parameters**

- val (int, bool, or str) the value for the const WireVector

- bitwidth (int) the desired bitwidth of the resulting const

- **signed** (*bool*) specify if bits should be used for two's complement

#### Returns

a WireVector object representing a const wire

Descriptions for all parameters not listed above can be found at WireVector.\_\_init\_\_()

For details of how constants are converted fron int, bool, and strings (for verilog constants), see documentation for the helper function infer\_val\_and\_bitwidth. Please note that a constant generated with signed=True is still just a raw bitvector and all arthimetic on it is unsigned by default. The signed=True argument is only used for proper inference of WireVector size and certain bitwidth sanity checks assuming a two's complement representation of the constants.

# 5.1.5 Conditionals

Conditional assignment of registers and WireVectors based on a predicate.

The management of selected assignments is expected to happen through the "with" blocks which will ensure that the region of execution for which the condition should apply is well defined. It is easiest to see with an example:

```

r1 = Register()

r2 = Register()

w3 = WireVector()

with conditional_assignment:

with a:

r1.next |= i  # set when a is true

with b:

r2.next |= j  # set when a and b are true

with c:

r1.next |= k  # set when a is false and c is true

r2.next |= k

with otherwise:

r2.next |= l  # a is false and c is false

with d:

w3.next |= m  # d is true (assignments must be independent)

```

This is equivalent to:

```

r1.next <<= select(a, i, select(c, k, default))

r2.next <<= select(a, select(b, j, default), select(c, k, l))

w3 <<= select(d, m, 0)</pre>

```

This functionality is provided through two instances: conditional\_update, which is a context manager (under which conditional assignments can be made), and otherwise, which is an instance that stands in for a 'fall through' case. The details of how these should be used, and the difference between normal assignments and conditional assignments, described in more detail in the state machine example in examples/example3-statemachine.py.

There are instances where you might want a wirevector to be set to a certain value in all but certain with blocks. For example, say you have a processor with a PC register that is normally updated to PC + 1 after each cycle, except when the current instruction is a branch or jump. You could represent that as follows:

```

pc = pyrtl.Register(32)

instr = pyrtl.WireVector(32)

res = pyrtl.WireVector(32)

op = instr[:7]

ADD = 0b0110011

JMP = 0b1101111

with conditional_assignment(

defaults={

pc: pc + 1,

res: 0

}

):

with op == ADD:

res |= instr[15:20] + instr[20:25]

# pc will be updated to pc + 1

with op == JMP:

pc.next |= pc + instr[7:]

# res will be set to 0

```

In addition to the conditional context, there is a helper function *currently\_under\_condition()* which will test if the code where it is called is currently elaborating hardware under a condition.

```

pyrtl.conditional.currently_under_condition()

```

Returns True if execution is currently in the context of a \_ConditionalAssignment.

```

pyrtl.otherwise = <pyrtl.conditional._Otherwise object>

```

Context providing functionality of PyRTL otherwise.

```

pyrtl.conditional_assignment = <pyrtl.conditional._ConditionalAssignment object>

```

# 5.2 Registers and Memories

# 5.2.1 Registers

The class *Register* is derived from *WireVector*, and so can be used just like any other *WireVector*. Reading a register produces the stored value available in the current cycle. The stored value for the following cycle can be set by assigning to property *next* with the <<= (\_\_ilshift\_\_()) operator. Registers reset to zero by default, and reside in the same clock domain.

class pyrtl.wire.Register(bitwidth, name=", reset\_value=None, block=None)

Bases: WireVector

A WireVector with a register state element embedded.

Registers only update their outputs on posedge of an implicit clock signal. The "value" in the current cycle can be accessed by just referencing the Register itself. To set the value for the next cycle (after the next posedge) you write to the property next with the <<= operator. For example, if you want to specify a counter it would look like: a.next <<= a + 1

```

__init__(bitwidth, name=", reset_value=None, block=None)

```

Construct a register.

#### **Parameters**

- **bitwidth** (*int*) Number of bits to represent this register.

- name (str) The name of the wire. Must be unique. If none is provided, one will be autogenerated.

- **reset\_value** Value to initialize this register to during simulation and in any code (e.g. Verilog) that is exported. Defaults to 0, but can be explicitly overridden at simulation time.

- block The block under which the wire should be placed. Defaults to the working block.

#### Returns

a WireVector object representing a register.

It is an error if the reset\_value cannot fit into the specified bitwidth for this register.

# property next

This property is the way to set what the WireVector will be the next cycle (aka, it is before the D-Latch)

# 5.2.2 Memories

MemBlock is the object for specifying block memories. It can be indexed like an array for both reading and writing. Writes under a conditional are automatically converted to enabled writes. For example, consider the following examples where addr, data, and we are all WireVectors:

```

data = memory[addr] # infer read port

memory[addr] <<= data # infer write port

mem[address] <<= MemBlock.EnabledWrite(data, enable=we)</pre>

```

When the address of a memory is assigned to using an *EnabledWrite* object items will only be written to the memory when the enable WireVector is set to high (1).

#### class EnabledWrite(data, enable)

Allows for an enable bit for each write port, where data (the first field in the tuple) is the normal data address, and enable (the second field) is a one bit signal specifying that the write should happen (i.e. active high).

#### data

Alias for field number 0

#### enable

Alias for field number 1

\_\_init\_\_(bitwidth, addrwidth, name=", max\_read\_ports=2, max\_write\_ports=1, asynchronous=False, block=None)

Create a PyRTL read-write memory.

#### **Parameters**

- bitwidth (int) Defines the bitwidth of each element in the memory

- addrwidth (int) The number of bits used to address an element of the memory. This also defines the size of the memory

- **name** (*basestring*) The identifier for the memory

- max\_read\_ports limits the number of read ports each block can create; passing *None* indicates there is no limit

- max\_write\_ports limits the number of write ports each block can create; passing *None* indicates there is no limit

- **asynchronous** (*bool*) If false make sure that memory reads are only done using values straight from a register. (aka make sure that the read is synchronous)

- name Name of the memory. Defaults to an autogenerated name

- **block** The block to add it to, defaults to the working block

It is best practice to make sure your block memory/fifos read/write operations start on a clock edge if you want them to synthesize into efficient hardware. MemBlocks will enforce this by making sure that you only address them with a register or input, unless you explicitly declare the memory as asynchronous with asynchronous=True flag. Note that asynchronous mems are, while sometimes very convenient and tempting, rarely a good idea. They can't be mapped to block RAMs in FPGAs and will be converted to registers by most design tools even though PyRTL can handle them with no problem. For any memory beyond a few hundred entries it is not a realistic option.

Each read or write to the memory will create a new *port* (either a read port or write port respectively). By default memories are limited to 2-read and 1-write port, but to keep designs efficient by default, but those values can be set as options. Note that memories with high numbers of ports may not be possible to map to physical memories such as block RAMs or existing memory hardware macros.

#### 5.2.3 **ROMs**

Bases: MemBlock

PyRTL Read Only Memory.

RomBlocks are the read only memory block for PyRTL. They support the same read interface and normal memories, but they are cannot be written to (i.e. there are no write ports). The ROM must be initialized with some values and construction through the use of the romdata which is the memory for the system.

\_\_init\_\_(bitwidth, addrwidth, romdata, name='', max\_read\_ports=2, build\_new\_roms=False, asynchronous=False, pad\_with\_zeros=False, block=None)

Create a Python Read Only Memory.

#### **Parameters**

- **bitwidth** (*int*) The bitwidth of each item stored in the ROM

- addrwidth (int) The bitwidth of the address bus (determines number of addresses)

- romdata This can either be a function or an array (iterable) that maps an address as an input to a result as an output

- **name** (str) The identifier for the memory

- max\_read\_ports limits the number of read ports each block can create; passing None indicates there is no limit

- **build\_new\_roms** (*bool*) indicates whether to create and pass new RomBlocks during \_\_getitem\_\_ to avoid exceeding *max\_read\_ports*

- **asynchronous** (*bool*) If false make sure that memory reads are only done using values straight from a register. (aka make sure that reads are synchronous)

- pad\_with\_zeros (boo1) If true, extend any missing romdata with zeros out until the size of the romblock so that any access to the rom is well defined. Otherwise, the simulation should throw an error on access of unintialized data. If you are generating verilog from the rom, you will need to specify a value for every address (in which case setting this to True will help), however for testing and simulation it useful to know if you are off the end of explicitly specified values (which is why it is False by default)

- **block** The block to add to, defaults to the working block

# 5.3 Simulation and Testing

#### 5.3.1 Simulation

A class for simulating blocks of logic step by step.

A Simulation step works as follows:

- 1. Registers are updated:

- 1. (If this is the first step) With the default values passed in to the Simulation during instantiation and/or any reset values specified in the individual registers.

- 2. (Otherwise) With their next values calculated in the previous step (r logic nets).

- 2. The new values of these registers as well as the values of block inputs are propagated through the combinational logic.

- 3. Memory writes are performed (@ logic nets).

- 4. The current values of all wires are recorded in the trace.

5. The next values for the registers are saved, ready to be applied at the beginning of the next step.

Note that the register values saved in the trace after each simulation step are from *before* the register has latched in its newly calculated values, since that latching in occurs at the beginning of the *next* step.

In addition to the functions methods listed below, it is sometimes useful to reach into this class and access internal state directly. Of particular usefulness are:

- .tracer: stores the SimulationTrace in which results are stored

- .value: a map from every signal in the block to its current simulation value

- .regvalue: a map from register to its value on the next tick

- .memvalue: a map from memid to a dictionary of address: value

\_\_init\_\_(tracer=True, register\_value\_map={}, memory\_value\_map={}, default\_value=0, block=None)

Creates a new circuit simulator.

#### **Parameters**

- tracer (SimulationTrace) Stores execution results. Defaults to a new SimulationTrace with no params passed to it. If None is passed, no tracer is instantiated (which is good for long running simulations). If the default (true) is passed, Simulation will create a new tracer automatically which can be referenced by the member variable .tracer

- register\_value\_map (dict[Register, int]) Defines the initial value for the registers specified; overrides the registers's reset\_value.

- memory\_value\_map Defines initial values for many addresses in a single or multiple memory. Format: {Memory: {address: Value}}. Memory is a memory block, address is the address of a value

- **default\_value** (*int*) The value that all unspecified registers and memories will initialize to (default 0). For registers, this is the value that will be used if the particular register doesn't have a specified reset\_value, and isn't found in the *register\_value\_map*.

- **block** (Block) the hardware block to be traced (which might be of type *PostSynthBlock*). Defaults to the working block

Warning: Simulation initializes some things when called with \_\_init\_\_(), so changing items in the block for Simulation will likely break the simulation.

#### inspect(w)

Get the value of a WireVector in the last simulation cycle.

#### **Parameters**

$\mathbf{w}$  ( $\mathbf{str}$ ) – the name of the WireVector to inspect (passing in a WireVector instead of a name is deprecated)

#### Returns

value of w in the current step of simulation

Will throw KeyError if w does not exist in the simulation.

#### Example:

```

sim.inspect('a') == 10  # returns value of wire 'a' at current step

```

## inspect\_mem(mem)

Get the values in a map during the current simulation cycle.

#### **Parameters**

**mem** – the memory to inspect

#### Returns

{address: value}

Note that this returns the current memory state. Modifying the dictonary will also modify the state in the simulator

#### step(provided inputs)

Take the simulation forward one cycle.

#### **Parameters**

provided\_inputs - a dictionary mapping WireVectors to their values for this step

A step causes the block to be updated as follows, in order:

- 1. Registers are updated with their *next* values computed in the previous cycle

- 2. Block inputs and these new register values propagate through the combinational logic

- 3. Memories are updated

- 4. The *next* values of the registers are saved for use in step 1 of the next cycle.

All input wires must be in the *provided\_inputs* in order for the simulation to accept these values.

Example: if we have inputs named a and x, we can call:

```

sim.step({'a': 1, 'x': 23})

```

to simulate a cycle with values 1 and 23 respectively.

**step\_multiple**(provided\_inputs={}, expected\_outputs={}, nsteps=None, file=<\_io.TextIOWrapper name='<stdout>' mode='w' encoding='utf-8'>, stop\_after\_first\_error=False)

Take the simulation forward N cycles, based on the number of values for each input

#### **Parameters**

- ullet provided\_inputs a dictionary mapping WireVectors to their values for N steps

- $\bullet$  expected\_outputs a dictionary mapping WireVectors to their expected values for N steps; use ? to indicate you don't care what the value at that step is

- **nsteps** number of steps to take (defaults to None, meaning step for each supplied input value)

- **file** where to write the output (if there are unexpected outputs detected)

- **stop\_after\_first\_error** a boolean flag indicating whether to stop the simulation after encountering the first error (defaults to False)

All input wires must be in the *provided\_inputs* in order for the simulation to accept these values. Additionally, the length of the array of provided values for each input must be the same.

When *nsteps* is specified, then it must be *less than or equal* to the number of values supplied for each input when *provided\_inputs* is non-empty. When *provided\_inputs* is empty (which may be a legitimate case for a design that takes no inputs), then *nsteps* will be used. When *nsteps* is not specified, then the simulation will take the number of steps equal to the number of values supplied for each input.

Example: if we have inputs named a and b and output o, we can call:

```

sim.step_multiple({'a': [0,1], 'b': [23,32]}, {'o': [42, 43]})

```

to simulate 2 cycles, where in the first cycle a and b take on 0 and 23, respectively, and o is expected to have the value 42, and in the second cycle a and b take on 1 and 32, respectively, and o is expected to have the value 43

If your values are all single digit, you can also specify them in a single string, e.g.:

```

sim.step_multiple({'a': '01', 'b': '01'})

```

will simulate 2 cycles, with a and b taking on 0 and 0, respectively, on the first cycle and 1 and 1, respectively, on the second cycle.

Example: if the design had no inputs, like so:

```

a = pyrtl.Register(8)

b = pyrtl.Output(8, 'b')

a.next <<= a + 1

b <<= a

sim = pyrtl.Simulation()

sim.step_multiple(nsteps=3)</pre>

```

Using sim.step\_multiple(nsteps=3) simulates 3 cycles, after which we would expect the value of b to be 2.

# 5.3.2 Fast (JIT to Python) Simulation

A class for running JIT-to-python implementations of blocks.

A Simulation step works as follows:

- 1. Registers are updated:

- 1. (If this is the first step) With the default values passed in to the Simulation during instantiation and/or any reset values specified in the individual registers.

- 2. (Otherwise) With their next values calculated in the previous step (r logic nets).

- 2. The new values of these registers as well as the values of block inputs are propagated through the combinational logic.

- 3. Memory writes are performed (@ logic nets).

- 4. The current values of all wires are recorded in the trace.

- 5. The next values for the registers are saved, ready to be applied at the beginning of the next step.

Note that the register values saved in the trace after each simulation step are from *before* the register has latched in its newly calculated values, since that latching in occurs at the beginning of the *next* step.

```

__init__(register_value_map={}, memory_value_map={}, default_value=0, tracer=True, block=None, code_file=None)

```

Instantiates a Fast Simulation instance.

The interface for FastSimulation and Simulation should be almost identical. In addition to the Simulation arguments, FastSimulation additionally takes:

#### **Parameters**

**code\_file** – The file in which to store a copy of the generated Python code. Defaults to no code being stored.

Look at Simulation.\_\_init\_\_() for descriptions for the other parameters.

This builds the Fast Simulation compiled Python code, so all changes to the circuit after calling this function will not be reflected in the simulation.

#### inspect(w)

Get the value of a WireVector in the last simulation cycle.

#### **Parameters**

$\mathbf{w}$  ( $\mathbf{str}$ ) – the name of the WireVector to inspect (passing in a WireVector instead of a name is deprecated)

#### Returns

value of w in the current step of simulation

Will throw KeyError if *w* is not being tracked in the simulation.

#### inspect\_mem(mem)

Get the values in a map during the current simulation cycle.

#### **Parameters**

mem – the memory to inspect

#### Returns

{address: value}

Note that this returns the current memory state. Modifying the dictonary will also modify the state in the simulator

## step(provided\_inputs)

Run the simulation for a cycle.

#### **Parameters**

```

provided_inputs – a dictionary mapping WireVectors (or their names) to their values for this step (eg: {wire: 3, "wire_name": 17})

```

A step causes the block to be updated as follows, in order:

- 1. Registers are updated with their *next* values computed in the previous cycle

- 2. Block inputs and these new register values propagate through the combinational logic

- 3. Memories are updated

- 4. The *next* values of the registers are saved for use in step 1 of the next cycle.

## Take the simulation forward N cycles, where N is the number of

values for each provided input.

#### **Parameters**

- provided\_inputs a dictionary mapping WireVectors to their values for N steps

- **expected\_outputs** a dictionary mapping WireVectors to their expected values for N steps; use ? to indicate you don't care what the value at that step is

- **nsteps** number of steps to take (defaults to None, meaning step for each supplied input value)

- **file** where to write the output (if there are unexpected outputs detected)

- **stop\_after\_first\_error** a boolean flag indicating whether to stop the simulation after the step where the first errors are encountered (defaults to False)

All input wires must be in the *provided\_inputs* in order for the simulation to accept these values. Additionally, the length of the array of provided values for each input must be the same.

When *nsteps* is specified, then it must be *less than or equal* to the number of values supplied for each input when *provided\_inputs* is non-empty. When *provided\_inputs* is empty (which may be a legitimate case for a design that takes no inputs), then *nsteps* will be used. When *nsteps* is not specified, then the simulation will take the number of steps equal to the number of values supplied for each input.

Example: if we have inputs named a and b and output o, we can call:

```

sim.step_multiple({'a': [0,1], 'b': [23,32]}, {'o': [42, 43]})

```

to simulate 2 cycles, where in the first cycle a and b take on 0 and 23, respectively, and o is expected to have the value 42, and in the second cycle a and b take on 1 and 32, respectively, and o is expected to have the value 43.

If your values are all single digit, you can also specify them in a single string, e.g.:

```

sim.step_multiple({'a': '01', 'b': '01'})

```

will simulate 2 cycles, with a and b taking on 0 and 0, respectively, on the first cycle and 1 and 1, respectively, on the second cycle.

Example: if the design had no inputs, like so:

```

a = pyrtl.Register(8)

b = pyrtl.Output(8, 'b')

a.next <<= a + 1

b <<= a

sim = pyrtl.Simulation()

sim.step_multiple(nsteps=3)</pre>

```

Using sim.step\_multiple(nsteps=3) simulates 3 cycles, after which we would expect the value of b to be 2.

# 5.3.3 Compiled (JIT to C) Simulation

Simulate a block, compiling to C for efficiency.

This module provides significant speed improvements over FastSimulation, at the cost of somewhat longer setup time. Generally this will do better than FastSimulation for simulations requiring over 1000 steps. It is not built to be a debugging tool, though it may help with debugging. Note that only Input and Output wires can be traced using CompiledSimulation. This code is still experimental, but has been used on designs of significant scale to good effect.

In order to use this, you need:

- A 64-bit processor

- GCC (tested on version 4.8.4)

- A 64-bit build of Python

If using the multiplication operand, only some architectures are supported:

- x86-64 / amd64

- · arm64 / aarch64

- mips64 (untested)

default\_value is currently only implemented for registers, not memories.

A Simulation step works as follows:

- 1. Registers are updated:

- 1. (If this is the first step) With the default values passed in to the Simulation during instantiation and/or any reset values specified in the individual registers.

- 2. (Otherwise) With their next values calculated in the previous step (r logic nets).

- 2. The new values of these registers as well as the values of block inputs are propagated through the combinational logic.

- 3. Memory writes are performed (@ logic nets).

- 4. The current values of all wires are recorded in the trace.

- 5. The next values for the registers are saved, ready to be applied at the beginning of the next step.

Note that the register values saved in the trace after each simulation step are from *before* the register has latched in its newly calculated values, since that latching in occurs at the beginning of the *next* step.

```

__init__(tracer=True, register_value_map={}, memory_value_map={}, default_value=0, block=None)

```

#### inspect(w)

Get the latest value of the wire given, if possible.

# inspect\_mem(mem)

Get a view into the contents of a MemBlock.

#### run(inputs)

Run many steps of the simulation.

#### **Parameters**

**inputs** – A list of input mappings for each step; its length is the number of steps to be executed.

# step(inputs)

Run one step of the simulation.

#### **Parameters**

**inputs** – A mapping from input names to the values for the step.

A step causes the block to be updated as follows, in order:

- 1. Registers are updated with their *next* values computed in the previous cycle

- 2. Block inputs and these new register values propagate through the combinational logic

- 3. Memories are updated

4. The *next* values of the registers are saved for use in step 1 of the next cycle.

```

step_multiple(provided_inputs={}, expected_outputs={}, nsteps=None, file=<_io.TextIOWrapper name='<stdout>' mode='w' encoding='utf-8'>, stop_after_first_error=False)

```

Take the simulation forward N cycles, where N is the number of values for each provided input.

#### **Parameters**

- provided\_inputs a dictionary mapping wirevectors to their values for N steps

- **expected\_outputs** a dictionary mapping wirevectors to their expected values for N steps; use ? to indicate you don't care what the value at that step is

- **nsteps** number of steps to take (defaults to None, meaning step for each supplied input value)

- **file** where to write the output (if there are unexpected outputs detected)

- **stop\_after\_first\_error** a boolean flag indicating whether to stop the simulation after the step where the first errors are encountered (defaults to False)

All input wires must be in the *provided\_inputs* in order for the simulation to accept these values. Additionally, the length of the array of provided values for each input must be the same.

When *nsteps* is specified, then it must be *less than or equal* to the number of values supplied for each input when *provided\_inputs* is non-empty. When *provided\_inputs* is empty (which may be a legitimate case for a design that takes no inputs), then *nsteps* will be used. When *nsteps* is not specified, then the simulation will take the number of steps equal to the number of values supplied for each input.

Example: if we have inputs named a and b and output o, we can call:

```

sim.step_multiple({'a': [0,1], 'b': [23,32]}, {'o': [42, 43]})

```

to simulate 2 cycles, where in the first cycle a and b take on 0 and 23, respectively, and o is expected to have the value 42, and in the second cycle a and b take on 1 and 32, respectively, and o is expected to have the value 43.

If your values are all single digit, you can also specify them in a single string, e.g.:

```

sim.step_multiple({'a': '01', 'b': '01'})

```

will simulate 2 cycles, with a and b taking on 0 and 0, respectively, on the first cycle and 1 and 1, respectively, on the second cycle.

Example: if the design had no inputs, like so:

```

a = pyrtl.Register(8)

b = pyrtl.Output(8, 'b')

a.next <<= a + 1

b <<= a

sim = pyrtl.Simulation()

sim.step_multiple(nsteps=3)</pre>

```

Using sim.step\_multiple(nsteps=3) simulates 3 cycles, after which we would expect the value of b to be 2.

# 5.3.4 Simulation Trace

class pyrtl.simulation.SimulationTrace(wires\_to\_track=None, block=None)

Storage and presentation of simulation waveforms.

```

__init__(wires_to_track=None, block=None)

```

Creates a new Simulation Trace

#### **Parameters**

- wires\_to\_track The wires that the tracer should track. If unspecified, will track all explicitly-named wires. If set to 'all', will track all wires, including internal wires.

- block Block containing logic to trace

```

add_fast_step(fastsim)

```

Add the fastsim context to the trace.

```

add_step(value_map)

```

Add the values in *value\_map* to the end of the trace.

Print performance counter statistics for trace names.

#### **Parameters**

- **trace\_names** (*str*) List of trace names. Each trace must be a single-bit wire.

- file The place to write output, defaults to stdout.

This function prints the number of cycles where each trace's value is one. This is useful for counting the number of times important events occur in a simulation, such as cache misses and branch mispredictions.

Prints a list of wires and their current values.

#### **Parameters**

- base (int) the base the values are to be printed in

- **compact** (*bool*) whether to omit spaces in output lines

```

print_vcd(file=<_io.TextIOWrapper name='<stdout>' mode='w' encoding='utf-8'>, include_clock=False)

Print the trace out as a VCD File for use in other tools.

```

#### **Parameters**

- **file** file to open and output vcd dump to.

- include\_clock boolean specifying if the implicit clk should be included.

Dumps the current trace to file as a value change dump file. The file parameter defaults to stdout and the *include\_clock* defaults to False.

# Examples:

```

sim_trace.print_vcd()

sim_trace.print_vcd("my_waveform.vcd", include_clock=True)

```

Render the trace to a file using unicode and ASCII escape sequences.

#### **Parameters**

- **trace\_list** (list[str]) A list of signal names to be output in the specified order.

- **file** The place to write output, default to stdout.

- renderer (WaveRenderer) An object that translates traces into output bytes.

- **symbol\_len** (int) The "length" of each rendered value in characters. If None, the length will be automatically set such that the largest represented value fits.

- repr\_func (Callable) Function to use for representing each value in the trace. Examples include hex, oct, bin, and str (for decimal), val\_to\_signed\_integer() (for signed decimal) or the function returned by enum\_name() (for IntEnum). Defaults to hex.

- **repr\_per\_name** (dict) Map from signal name to a function that takes in the signal's value and returns a user-defined representation. If a signal name is not found in the map, the argument **repr\_func** will be used instead.

- **segment\_size** (int) Traces are broken in the segments of this number of cycles.

The resulting output can be viewed directly on the terminal or looked at with **more** or **less -R** which both should handle the ASCII escape sequences used in rendering.

# 5.3.5 Wave Renderer

class pyrtl.simulation.WaveRenderer(constants)

Render a SimulationTrace to the terminal.

See examples/renderer-demo.py, which renders traces with various options. You can choose a default renderer by exporting the PYRTL\_RENDERER environment variable. See the documentation for subclasses of RendererConstants.

```

__init__(constants)

```

Instantiate a WaveRenderer.

#### **Parameters**

**constants** – Subclass of RendererConstants that specifies the ASCII/Unicode characters to use for rendering waveforms.

```

pyrtl.simulation.enum_name(EnumClass)

```

Returns a function that returns the name of an enum value as a string.

Use enum\_name as a repr\_func or repr\_per\_name for SimulationTrace.render\_trace() to display enum names, instead of their numeric value, in traces. Example:

```

class State(enum.IntEnum):

F00 = 0

BAR = 1

state = Input(name='state', bitwidth=1)

sim = Simulation()

sim.step_multiple({'state': [State.F00, State.BAR]})

```

(continues on next page)

(continued from previous page)

#### **Parameters**

**EnumClass** (type) — enum to convert. This is the enum class, like State, not an enum value, like State.FOO or 1.

### **Return type**

Callable[[int], str]

#### Returns

A function that accepts an enum value, like State.FOO or 1, and returns the value's name as a string, like 'FOO'.

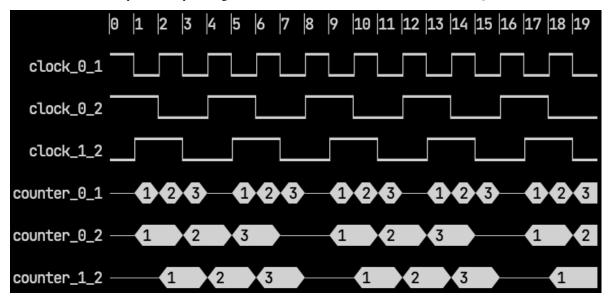

## class pyrtl.simulation.PowerlineRendererConstants

Bases: Utf8RendererConstants

Powerline renderer constants. Font must include powerline glyphs.

This render is closest to a traditional logic analyzer. Single-bit WireVectors are rendered as square waveforms, with vertical rising and falling edges. Multi-bit WireVector values are rendered in reverse-video hexagons.

This renderer requires a terminal font that supports Powerline glyphs

Enable this renderer by default by setting the PYRTL\_RENDERER environment variable to powerline.

#### class pyrtl.simulation.Utf8RendererConstants

Bases: RendererConstants

UTF-8 renderer constants. These should work in most terminals.

Single-bit WireVectors are rendered as square waveforms, with vertical rising and falling edges. Multi-bit WireVector values are rendered in reverse-video rectangles.

This is the default renderer on non-Windows platforms.

Enable this renderer by default by setting the PYRTL\_RENDERER environment variable to utf-8.

class pyrtl.simulation.Utf8AltRendererConstants

Bases: RendererConstants

Alternative UTF-8 renderer constants.

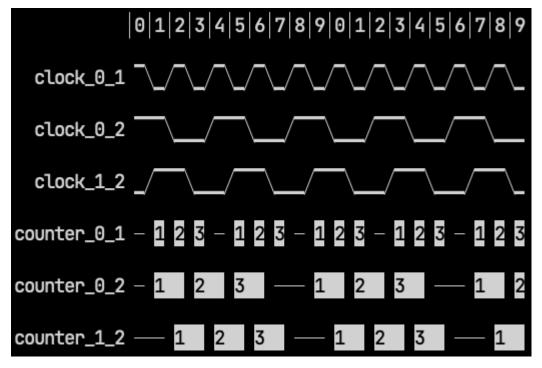

Single-bit WireVectors are rendered as waveforms with sloped rising and falling edges. Multi-bit WireVector values are rendered in reverse-video rectangles.

Compared to *Utf8RendererConstants*, this renderer is more compact because it uses one character between cycles instead of two.

$Enable\ this\ renderer\ by\ default\ by\ setting\ the\ PYRTL\_RENDERER\ environment\ variable\ to\ \verb"utf-8-alt".$

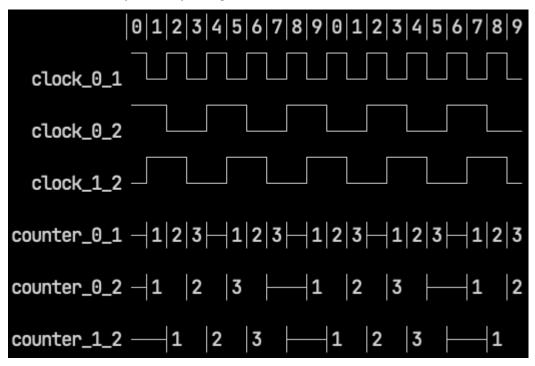

### class pyrtl.simulation.Cp437RendererConstants

Bases: RendererConstants

Code page 437 renderer constants (for windows cmd compatibility).

Single-bit WireVectors are rendered as square waveforms, with vertical rising and falling edges. Multi-bit WireVector values are rendered between vertical bars.

Code page 437 is also known as 8-bit ASCII. This is the default renderer on Windows platforms.

Compared to *Utf8RendererConstants*, this renderer is more compact because it uses one character between cycles instead of two, but the wire names are vertically aligned at the bottom of each waveform.

Enable this renderer by default by setting the PYRTL\_RENDERER environment variable to cp437.

# class pyrtl.simulation.AsciiRendererConstants

Bases: RendererConstants

7-bit ASCII renderer constants. These should work anywhere.

Single-bit WireVectors are rendered as waveforms with sloped rising and falling edges. Multi-bit WireVector values are rendered between vertical bars.

Enable this renderer by default by setting the PYRTL\_RENDERER environment variable to ascii.

# 5.4 Logic Nets and Blocks

# 5.4.1 LogicNets

class pyrtl.core.LogicNet(op, op\_param, args, dests)

The basic immutable datatype for storing a "net" in a netlist.

This is used for the internal representation that Python stores knowledge of what this is, and how it is used is only required for advanced users of PyRTL.

A 'net' is a structure in Python that is representative of hardware logic operations. These include binary operations, such as *and or* and *not*, arithmetic operations such as + and -, as well as other operations such as Memory ops, and concat, split, wire, and reg logic.

The details of what is allowed in each of these fields is defined in the comments of *Block*, and is checked by *Block.sanity\_check()*

**Logical Operations:**

| ор | op_param | args   | dests |                                                                                                                              |

|----|----------|--------|-------|------------------------------------------------------------------------------------------------------------------------------|

| &  | None     | a1, a2 | out   | AND two wires together, put result into <i>out</i>                                                                           |

| I  | None     | a1, a2 | out   | OR two wires together, put result into <i>out</i>                                                                            |

| ۸  | None     | a1, a2 | out   | XOR two wires together, put result into <i>out</i>                                                                           |

| n  | None     | a1, a2 | out   | NAND two wires together, put result into <i>out</i>                                                                          |

| ~  | None     | a1     | out   | invert one wire, put result into <i>out</i>                                                                                  |

| +  | None     | a1, a2 | out   | add a1 and a2, put result into out len(out) == max(len(a1), len(a2)) + 1 works with both unsigned and two's complement       |

| -  | None     | a1, a2 | out   | subtract a2 from a1, put result into out len(out) == max(len(a1), len(a2)) + 1 works with both unsigned and two's complement |

| *  | None     | a1, a2 | out   | multiply al & a2, put result into out len(out) == len(a1) + len(a2) assumes un- signed, but signed_mult() provides wrapper   |

| =  | None     | a1, a2 | out   | check a1 & a2 equal, put result into out (0   1)                                                                             |

| <  | None     | a1, a2 | out   | check $a2$ greater than $a1$ , put result into $out (0   1)$                                                                 |

| >  | None     | a1, a2 | out   | check $a1$ greater than $a2$ , put result into $out (0   1)$                                                                 |

| W  | None     | w1     | w2    | connects w1 to w2 directional wire                                                                                           |

Chapter 5. Reference Guide logical operation

# 5.4.2 Blocks

# class pyrtl.core.Block

Block encapsulates a netlist.

A Block in PyRTL is the class that stores a netlist and provides basic access and error checking members. Each block has well defined inputs and outputs, and contains both the basic logic elements and references to the wires and memories that connect them together.

The logic structure is primarily contained in Block.logic which holds a set of *LogicNets*. Each *LogicNet* describes a primitive operation (such as an adder or memory). The primitive is described by a 4-tuple of:

- 1) the op (a single character describing the operation such as + or r),

- 2) a set of hard-wired *op\_params* (such as the constants to select from the "selection" op).

- 3) the tuple args which list the WireVectors hooked up as inputs to this particular net.

- 4) the tuple dests which list the WireVectors hooked up as output for this particular net.

Below is a list of the basic operations. These properties (more formally specified) should all be checked by the class method *Block.sanity\_check()*.

• Most logical and arithmetic ops are pretty self explanatory. Each takes exactly two arguments, and they should perform the arithmetic or logical operation specified.

```

OPS: &, |, ^, n, ~, +, -, *.

```

All inputs must be the same bitwidth. Logical operations produce as many bits as are in the input, while + and - produce n+1 bits, and \* produces 2n bits.

- In addition there are some operations for performing comparisons that should perform the operation specified. The = op is checking to see if the bits of the vectors are equal, while < and > do unsigned arithmetic comparison. All comparisons generate a single bit of output (1 for true, 0 for false).

- The w operator is simply a directional wire and has no logic function.

- The x operator is a multiplexer which takes a select bit and two signals. If the value of the select bit is 0 it selects the second argument; if it is 1 it selects the third argument. Select must be a single bit, while the other two arguments must be the same length.

- The c operator is the concatenation operator and combines any number of WireVectors (a, b, ..., z) into a single new WireVector with a in the MSB and z (or whatever is last) in the LSB position.

- The s operator is the selection operator and chooses, based on the *op\_param* specified, a subset of the logic bits from a WireVector to select. Repeats are accepted.

- The r operator is a register and on posedge, simply copies the value from the input to the output of the register.

- The m operator is a memory block read port, which supports async reads (acting like combinational logic). Multiple read (and write) ports are possible to the same memory but each m defines only one of those. The *op\_param* is a tuple containing two references: the mem id, and a reference to the MemBlock containing this port. The MemBlock should only be used for debug and sanity checks. Each read port has one *addr* (an arg) and one *data* (a dest).

- The @ (update) operator is a memory block write port, which supports synchronous writes (writes are "latched" at positive edge). Multiple write (and read) ports are possible to the same memory but each @ defines only one of those. The *op\_param* is a tuple containing two references: the mem id, and a reference to the MemoryBlock. Writes have three args (*addr*, *data*, and write enable *we\_en*). The dests should be an empty tuple. You will not see a written value change until the following cycle. If multiple writes happen to the same address in the same cycle the behavior is currently undefined.

The connecting elements (args and dests) should be WireVectors or derived from WireVector, and should be registered with the block using <code>Block.add\_wirevector()</code>. Nets should be registered using <code>Block.add\_net()</code>.

In addition, there is a member Block.legal\_ops which defines the set of operations that can be legally added to the block. By default it is set to all of the above defined operations, but it can be useful in certain cases to only allow a subset of operations (such as when transforms are being done that are "lowering" the blocks to more primitive ops).

# pyrtl.core.working\_block(block=None)

Convenience function for capturing the current working block.

If a block is not passed, or if the block passed is None, then this will return the "current working block". However, if a block is passed in it will simply return that block instead. This feature is useful in allowing functions to "override" the current working block.

# pyrtl.core.reset\_working\_block()

Reset the working block to be empty.

```

pyrtl.core.set_working_block(block, no_sanity_check=False)

```

Set the working block to be the block passed as argument. Compatible with the with statement.

Sanity checks will only be run if the new block is different from the original block.

```

pyrtl.core.temp_working_block()

```

Set the working block to be new temporary block.

If used with the *with* statement the block will be reset to the original value (at the time of call) at exit of the context.

```

pyrtl.core.Block.add_wirevector(self, wirevector)

```

Add a WireVector object to the block.

# **Parameters**

wirevector (WireVector) - WireVector object added to block

```

pyrtl.core.Block.remove_wirevector(self, wirevector)

```

Remove a WireVector object from the block.

# **Parameters**

wirevector (WireVector) - WireVector object removed from block

```

pyrtl.core.Block.add_net(self, net)

```

Add a net to the logic of the block.

#### **Parameters**

```

net (LogicNet) – LogicNet object added to block

```

The passed net, which must be of type LogicNet, is checked and then added to the block. No wires are added by this member, they must be added seperately with <code>Block.add\_wirevector()</code>.

```

pyrtl.core.Block.get_memblock_by_name(self, name, strict=False)

```

Get a reference to a memory stored in this block by name.

#### **Parameters**

- name (str) name of MemBlock object

- **strict** (*bool*) Determines if PyrtlError or None is thrown on no match. Defaults to False.

# Returns

a MemBlock object with specified name

By fallthrough, if a matching MemBlock cannot be found the value None is returned. However, if the argument strict is set to True, then this will instead throw a PyrtlError when no match is found.

This useful for when a block defines its own internal memory block, and during simulation you want to instantiate that memory with certain values for testing. Since the Simulation constructor requires a reference to the memory object itself, but the block you're testing defines the memory internally, this allows you to get the object reference.

Note that this requires you know the name of the memory block, meaning that you most likely need to have named it yourself.

# Example:

```

def special_memory(read_addr, write_addr, data, wen):

mem = pyrtl.MemBlock(bitwidth=32, addrwidth=5, name='special_mem')

mem[write_addr] <<= pyrtl.MemBlock.EnabledWrite(data, wen & (write_addr > 0))

return mem[read_addr]

read_addr = pyrtl.Input(5, 'read_addr')

write_addr = pyrtl.Input(5, 'write_addr')

data = pyrtl.Input(32, 'data')

wen = pyrtl.Input(1, 'wen')

res = pyrtl.Output(32, 'res')

res <<= special_memory(read_addr, write_addr, data, wen)</pre>

# Can only access it after the `special_memory` block has been instantiated/called

special_mem = pyrtl.working_block().get_memblock_by_name('special_mem')

sim = pyrtl.Simulation(memory_value_map={

special_mem: {

0: 5,

1: 6,

2: 7,

}

})

inputs = {

'read_addr': '012012',

'write_addr': '012012'.

'data':

'890333',

'wen':

'111000'.

}

expected = {

'res': '567590',

sim.step_multiple(inputs, expected)

```

pyrtl.core.Block.wirevector\_subset(self, cls=None, exclude=())

Return set of WireVectors, filtered by the type or tuple of types provided as *cls*.

# **Parameters**

- cls Type of returned WireVector objects

- exclude Type of WireVector objects to exclude

## Returns

Set of WireVector objects that are both a cls type and not a excluded type

If no *cls* is specified, the full set of WireVectors associated with the Block are returned. If *cls* is a single type, or a tuple of types, only those WireVectors of the matching types will be returned. This is helpful for getting all inputs, outputs, or registers of a block for example.

# Examples:

```

inputs = pyrtl.working_block().wirevector_subset(pyrtl.Input)

outputs = pyrtl.working_block().wirevector_subset(pyrtl.Output)

# returns set of all non-input WireVectors

non_inputs = pyrtl.working_block().wirevector_subset(exclude=pyrtl.Input)

```

```

pyrtl.core.Block.logic_subset(self, op=None)

```

Return set of LogicNets, filtered by the type(s) of logic op provided as op.

# **Parameters**

**op** – Operation of LogicNet to filter by. Defaults to None.

#### Returns

set of LogicNets with corresponding op

If no *op* is specified, the full set of LogicNets associated with the Block are returned. This is helpful for getting all memories of a block for example.

```

pyrtl.core.Block.get_wirevector_by_name(self, name, strict=False)

```

Return the WireVector matching name.

#### **Parameters**

- name (str) name of WireVector object

- **strict** (*bool*) Determines if PyrtlError or None is thrown on no match. Defaults to False.

# Returns

a WireVector object with specified name

By fallthrough, if a matching WireVector cannot be found the value None is returned. However, if the argument strict is set to True, then this will instead throw a PyrtlError when no match is found.

```

pyrtl.core.Block.net_connections(self, include_virtual_nodes=False)

```

Returns a representation of the current block useful for creating a graph.

## **Parameters**

**include\_virtual\_nodes** (*bool*) – if enabled, the wire itself will be used to signal an external source or sink (such as the source for an Input net). If disabled, these nodes will be excluded from the adjacency dictionaries

# Returns

Two dictionaries: one that maps WireVectors to the logic net that creates their signal (wire\_src\_dict) and one that maps WireVectors to a list of logic nets that use the signal (wire\_sink\_dict).

These dictionaries make the creation of a graph much easier, as well as facilitate other places in which one would need wire source and wire sink information.

Look at net\_graph() for one such graph that uses the information from this function.

```

pyrtl.core.Block.sanity_check(self)

```

Check block and throw PyrtlError or PyrtlInternalError if there is an issue.

Should not modify anything, only check data structures to make sure they have been built according to the assumptions stated in the Block comments.

# 5.5 Helper Functions

# 5.5.1 Cutting and Extending WireVectors

The functions below provide ways of combining, slicing, and extending *WireVectors* in ways that are often useful in hardware design. The functions below extend those member functions of the *WireVector* class itself (which provides support for the Python builtin len, slicing e.g. wire[3:6], zero\_extended(), sign\_extended(), and many operators such as addition and multiplication).

```

pyrtl.corecircuits.concat(*args)

```

Concatenates multiple WireVectors into a single WireVector.

#### **Parameters**

```

args (WireVector) - inputs to be concatenated

```

### Returns

WireVector with length equal to the sum of the args' lengths

You can provide multiple arguments and they will be combined with the right-most argument being the least significant bits of the result. Note that if you have a list of arguments to concat together you will likely want index 0 to be the least significant bit and so if you unpack the list into the arguments here it will be backwards. The function <code>concat\_list()</code> is provided for that case specifically.

Example using concat to combine two bytes into a 16-bit quantity:

```

concat(msb, lsb)

```

```

pyrtl.corecircuits.concat_list(wire list)

```

Concatenates a list of WireVectors into a single WireVector.

### **Parameters**

```

wire_list (list[WireVector]) - list of WireVectors to concat

```

# Returns

WireVector with length equal to the sum of the args' lengths

This take a list of WireVectors and concats them all into a single WireVector with the element at index 0 serving as the least significant bits. This is useful when you have a variable number of WireVectors to concatenate, otherwise *concat()* is prefered.

Example using concat\_list to combine two bytes into a 16-bit quantity:

```

mylist = [lsb, msb]

concat_list(mylist)

```

```

pyrtl.corecircuits.match_bitwidth(*args, **opt)

```

Matches the argument wires' bitwidth via zero or sign extension, returning new WireVectors

# **Parameters**

• args (WireVector) - WireVectors of which to match bitwidths

• **opt** – Optional keyword argument **signed=True** (defaults to False)

#### Returns

tuple of args in order with extended bits

Example of matching the bitwidths of two WireVectors a and b with zero extension:

```

a, b = match_bitwidth(a, b)

```

Example of matching the bitwidths of three WireVectors a, b, and c with with sign extension:

```

a, b, c = match_bitwidth(a, b, c, signed=True)

```

pyrtl.helperfuncs.truncate(wirevector\_or\_integer, bitwidth)

Returns a WireVector or integer truncated to the specified bitwidth

#### **Parameters**

- wirevector\_or\_integer Either a WireVector or an integer to be truncated.

- bitwidth (int) The length to which the first argument should be truncated.

#### Returns

A truncated WireVector or integer as appropriate.

This function truncates the most significant bits of the input, leaving a result that is only *bitwidth* bits wide. For integers this is performed with a simple bitmask of size *bitwidth*. For WireVectors the function calls *WireVector*. *truncate()* and returns a WireVector of the specified *bitwidth*.

## Examples:

```

truncate(9,3) # returns 1 (0b1001 truncates to 0b001)

truncate(5,3) # returns 5 (0b101 truncates to 0b101)

truncate(-1,3) # returns 7 (-0b1 truncates to 0b111)

y = truncate(x+1, x.bitwidth) # y.bitwdith will equal x.bitwidth

```

pyrtl.helperfuncs.chop(w, \*segment\_widths)

Returns a list of WireVectors, each a slice of the original w.

# **Parameters**

- w (WireVector) The WireVector to be chopped up into segments

- **segment\_widths** (*int*) Additional arguments are integers which are bitwidths

# Returns

A list of WireVectors each with a proper segment width

# Return type

List[WireVector]

This function chops a WireVector into a set of smaller WireVectors of different lengths. It is most useful when multiple "fields" are contained with a single WireVector, for example when breaking apart an instruction. For example, if you wish to break apart a 32-bit MIPS I-type (Immediate) instruction you know it has an 6-bit opcode, 25-bit operands, and 16-bit offset. You could take each of those slices in absolute terms: offset=instr[0:16], rt=instr[16:21] and so on, but then you have to do the arithmetic yourself. With this function you can do all the fields at once which can be seen in the examples below.

As a check, chop will throw an error if the sum of the lengths of the fields given is not the same as the length of the WireVector to chop. Note also that chop assumes that the "rightmost" arguments are the least significant bits (just like *concat()*) which is normal for hardware functions but makes the list order a little counter intuitive.

# Examples:

```

opcode, rs, rt, offset = chop(instr, 6, 5, 5, 16) # MIPS I-type instruction opcode, instr_index = chop(instr, 6, 26) # MIPS J-type instruction opcode, rs, rt, rd, sa, function = chop(instr, 6, 5, 5, 5, 5, 6) # MIPS R-type msb, middle, lsb = chop(data, 1, 30, 1) # break out the most and least significant.

bits

```

# pyrtl.helperfuncs.wire\_struct(wire\_struct\_spec)

Decorator that assigns names to WireVector slices.

@wire\_struct assigns names to non-overlapping WireVector slices. Suppose we have an 8-bit wide WireVector called byte. We can refer to all 8 bits with the name byte, but @wire\_struct lets us refer to slices by name, for example we could name the high 4 bits byte.high and the low 4 bits byte.low. Without @wire\_struct, we would refer to these slices as byte[4:8] and byte[0:4], which are prone to off-by-one errors and harder to read.

The example Byte @wire\_struct can be defined as:

```

@wire_struct

class Byte:

high: 4 # 'high' is name for the 4 most significant bits.

low: 4 # 'low' is name for the 4 least significant bits.

```

#### Construction

Once a @wire\_struct class is defined, it can be instantiated by providing drivers for all of its wires. This can be done in two ways:

1. Provide a driver for *each* component wire, for example:

```

byte = Byte(high=0xA, low=0xB)

```

Note how the component names (high, low) are used as keyword args for the constructor. Drivers must be provided for *all* components.

2. Provide a driver for the entire @wire\_struct, for example:

```

byte = Byte(Byte=0xAB)

```

Note how the class name (Byte) is used as a keyword arg for the constructor.

# **Accessing Slices**

After instantiating a @wire\_struct, the instance functions as a WireVector containing all the wires. For example, byte functions as a WireVector with bitwidth 8:

```

byte = Byte(Byte=0xAB)

print(byte.bitwidth) # Prints 8.

```

The named slice can be accessed through the . operator (\_\_getattr\_\_), for example byte.high and byte. low, which both function as WireVector with bitwidth 4:

```

byte = Byte(Byte=0xAB)

print(byte.high.bitwidth) # Prints 4.

print(byte.low.bitwidth) # Prints 4.

```

Both the instance and the slices are first-class WireVector, so they can be manipulated with all the usual PyRTL operators.

**Note:** len(byte) returns the number of components in the @wire\_struct (2), not the total bitwidth (8 == 4 + 4). To get the total bitwidth, use byte.bitwidth or len(as\_wires(byte)).

# **Naming**

A @wire\_struct can be assigned a name in the usual way:

```

byte = Byte(name='b', high=0xC, low=0xD)

byte = Byte(name='b', Byte=0xCD)

```

When a @wire\_struct is assigned a name (b), its components will be assigned dotted names (b.high, b.low):

```

print(byte.high.name) # Prints 'b.high'.

print(byte.low.name) # Prints 'b.low'.

```

**Warning:** All @wire\_struct names are only set during construction. You can later rename a @wire\_struct or its components, but those changes are local, and will not propagate to other @wire\_struct components. Renaming a @wire\_struct or its components is strongly discouraged.

# Composition

<code>@wire\_struct</code> can be composed with itself, and with wire\_matrix. For example, we can define a Pixel that contains three Byte:

```

@wire_struct

class Pixel:

red: Byte

green: Byte

blue: Byte

```

Drivers must be specified for all components, but they can be specified at any level. All these examples construct an equivalent @wire\_struct:

Hierarchical @wire\_struct components are accessed by composing . operators:

```

pixel pixel.red pixel.red.high pixel.red.low pixel.green pixel.green.high pixel.green.low pixel.blue pixel.blue.high pixel.blue.high pixel.blue.high pixel.blue.high pixel.blue.how

```

@wire\_struct can be composed with wire\_matrix:

```

Word = wire_matrix(component_schema=8, size=4)

@wire_struct

class CacheLine:

address: Word

data: Word

valid: 1

cache_line = CacheLine(address=0x01234567, data=0x89ABCDEF, valid=1)

```

Leaf-level components can be accessed by combining the . and [] operators, for example cache\_line. address[3].

# **Types**

You can change the type of a @wire\_struct's components to a WireVector subclass like Input or Output with the component\_type constructor argument:

You can also change the type of the @wire\_struct itself with the concatenated\_type cnstructor argument:

```

# Generates an Input named ``input_byte``.

input_byte = Byte(name='input_byte', concatenated_type=pyrtl.Input)

```

**Note:** No values are specified for input\_byte because its value is not known until simulation time.

```

pyrtl.helperfuncs.wire_matrix(component_schema, size)

```

Returns a class that assigns numbered indices to WireVector slices.